Research

Selahattin Sayil, Ph.D.

Professor

Research Interests

- Radiation Effects Modeling in Integrated Circuits

- Circuit Level Soft Error Hardening

- Low Power Design & Reliability Analysis

- Interconnect Modeling and Noise Prediction

- Crosstalk Delay Modeling and Prediction

- Contactless VLSI Testing

Current Research Projects

- "Thermal-Aware Hardening for Advanced CMOS Circuits”: Thermal effects have important implications for both performance and reliability of chips. If the impact of temperature is not taken into consideration, the mitigation efforts may fail which would lead to a significantly greater reliability issue for advanced technologies. For military applications, the effects can be much worse since the integrated circuits needs to function over a wide range of temperatures ranging from -55℃ to 125 ℃. By identifying the impact of of thermal effects, design principles will also be developed for other radiation hardening methodologies currently being used in avionics and space and military applications which will greatly benefit the industry.

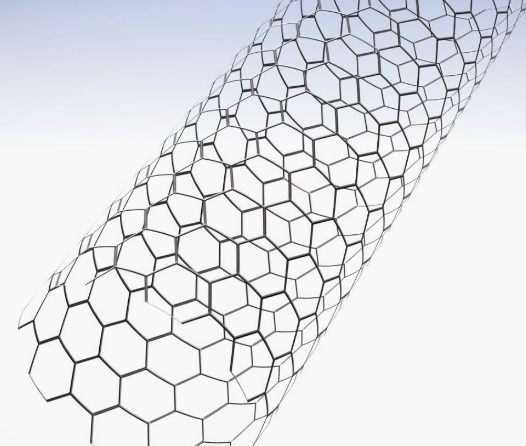

- "Modeling the Impact of Temperature on Single-Walled Carbon Nanotube Interconnects": Carbon nanotubes (CNTs) are graphene sheets rolled up into cylinders with diameter of the order of a nanometer.. By using CNT bundles overall resistance is reduced and it enables CNT based interconnect to replace conventional copper interconnects at advanced VLSI technology nodes. Several studies have investigated the electro-thermal transport in metallic SWCNTs for the applications of interconnect. Researchers have compared the performance of CNT-bundle interconnects to that of copper interconnects and found that there were significant performance improvements for intermediate and long interconnects. In our research, the crosstalk noise between SWCNT bundle interconnects with temperature independent and thermally aware model will be investigated. We will develop an efficient computational model for crosstalk estimation in identically coupled SWCNT bundle interconnects.

-

"Design of Asynchronous Circuits for Robustness in Deep Submicron CMOS Circuits": As the conventional CMOS scales down, the combinational logic will become susceptible to soft errors.. A more robust solution would be the use Asynchronous Circuits for soft errors and for process, supply voltage, and temperature variations. In this project, the feasibility of designing quasi-delay insensitive (QDI) asynchronous circuits for high soft error tolerance will be investigated. The behavior of Null Convention Logic (NCL) circuits in the presence of particle strikes will also be analyzed.

-

"Rad-Hard Circuit Design": My research focuses on designing radiation-hardened integrated circuits (ICs) that can operate reliably in harsh environments, such as space, nuclear facilities, and high-energy physics experiments like those at CERN. I explore ways to make circuits more robust by improving the design at both the device and system levels. This includes techniques like adding redundancy, using special types of memory elements, and designing circuits that are less sensitive to radiation damage. I work on both digital and mixed-signal circuits that can continue functioning even when exposed to high levels of radiation.

External Funding Received:

- Sayil, S. (PI), Tcheslavski, G. (co-PI) and Yoo, Julia (co-PI), “Promoting engaged and active learning through collaborative online lab experiences”, NSF IUSE (Improving Undergraduate STEM Education) program, Funding period” Sept. 1, 2021- Aug. 31, 2024, $294,097.

- Sayil, S., PI, (no co-PI), "Enhancing Student Learning via Value Added Engineering Education (VAEE)", Ecommons-Academic Partnerships, Funding Period: 11/20/2015- 6/30/2016- $4,116

- Sayil, S., PI, (no co-PI), “Low Power Radiation Tolerant VLSI Design for Advanced Spacecraft”, NASA/ TSGC New Investigations Program (NIP), October 2010, $9,000

- Sayil, S. PI, “Space Radiation Effects on Technology and Human Biology and Proper Mitigation Techniques”, NASA/TSGC (Texas Space Grant Consortium) Higher Education, September 2008-August 2010, $15,000