Research

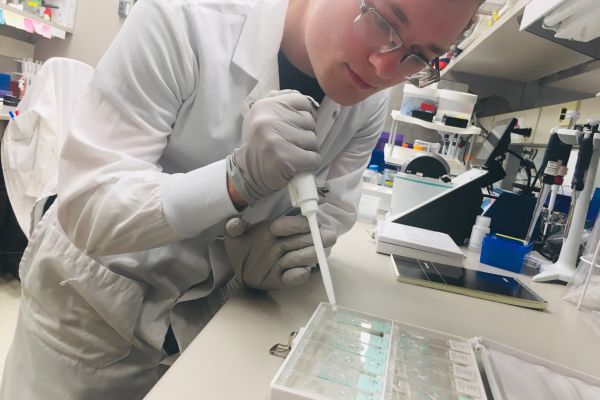

At Lamar University our research efforts make a hands-on difference in the lives of the people we serve. From NASA experiments to cutting-edge research in engineering, nursing, business, the arts, sciences and more, Lamar students and faculty are changing the way we see the world around us.

Research Centers

Research News

April 02, 2024

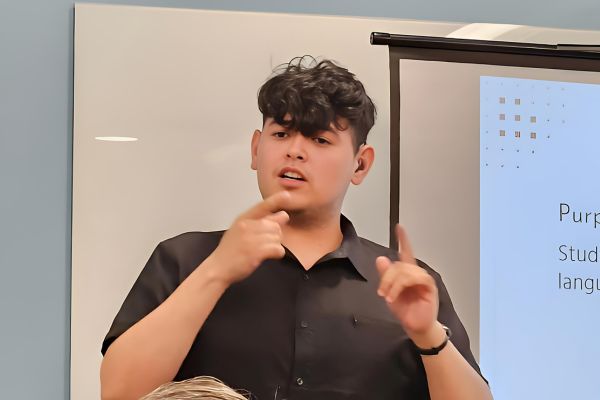

Lamar University's College of Graduate Studies hosted its second Graduate Research Conference on March 28, focusing on Artificial Intelligence (AI) and providing attendees with presentations, workshops, and discussions, aiming to enhance research skills and engagement among students and faculty,

Read More